16-Lagen-Leiterplatten bieten die Komplexität und Flexibilität, die moderne elektronische Geräte erfordern. Ein geschicktes Design und die Auswahl der Stapelreihenfolgen und Verbindungsmethoden zwischen den Schichten sind entscheidend für die Erzielung einer optimalen Leiterplattenleistung. In diesem Artikel gehen wir auf Überlegungen, Richtlinien und Best Practices ein, um Designern und Ingenieuren bei der Entwicklung effizienter und zuverlässiger 16-Lagen-Leiterplatten zu helfen.

1. Die Grundlagen der Stapelreihenfolge von 16-Lagen-Leiterplatten verstehen

1.1 Definition und Zweck der Stapelreihenfolge

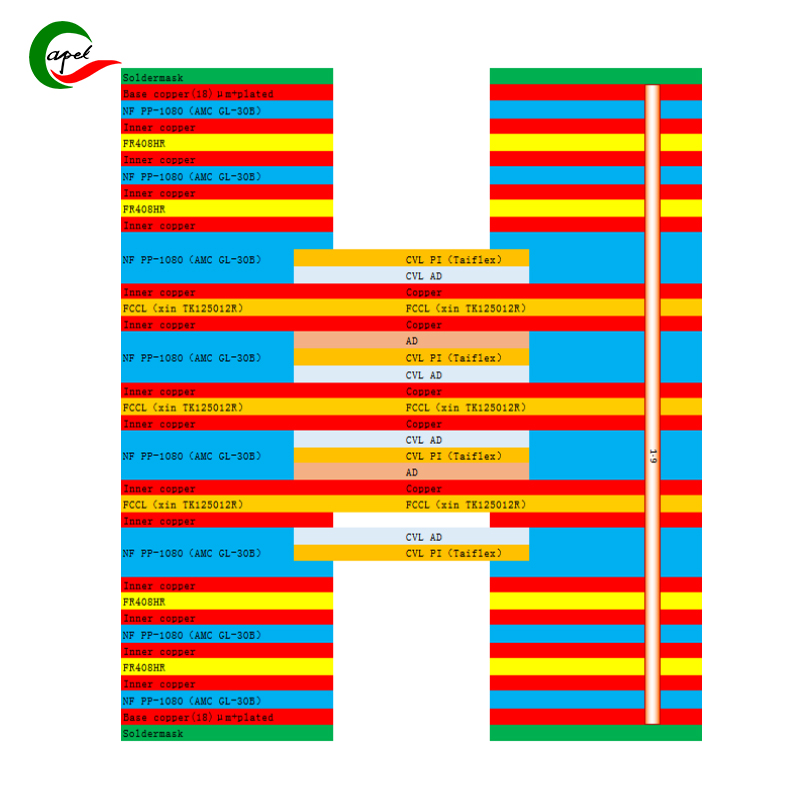

Die Stapelreihenfolge bezieht sich auf die Anordnung und Reihenfolge, in der Materialien wie Kupfer- und Isolierschichten zusammenlaminiert werden, um eine mehrschichtige Leiterplatte zu bilden. Die Stapelreihenfolge bestimmt die Platzierung von Signalschichten, Leistungsschichten, Erdungsschichten und anderen wichtigen Komponenten der Stapel.

Der Hauptzweck der Stapelreihenfolge besteht darin, die erforderlichen elektrischen und mechanischen Eigenschaften der Platine zu erreichen. Es spielt eine entscheidende Rolle bei der Bestimmung der Impedanz, der Signalintegrität, der Stromverteilung, des Wärmemanagements und der Machbarkeit einer Leiterplatte. Die Stapelreihenfolge beeinflusst auch die Gesamtleistung, Zuverlässigkeit und Herstellbarkeit der Platine.

1.2 Faktoren, die das Design der Stapelreihenfolge beeinflussen: Bei der Gestaltung der Stapelreihenfolge von a sind mehrere Faktoren zu berücksichtigen

16-Lagen-Leiterplatte:

a) Elektrische Überlegungen:Die Anordnung der Signal-, Strom- und Masseebenen sollte optimiert werden, um eine ordnungsgemäße Signalintegrität, Impedanzkontrolle und Reduzierung elektromagnetischer Störungen sicherzustellen.

b) Thermische Überlegungen:Die Platzierung von Strom- und Masseebenen sowie die Einbeziehung thermischer Durchkontaktierungen tragen dazu bei, die Wärme effektiv abzuleiten und die optimale Betriebstemperatur der Komponente aufrechtzuerhalten.

c) Herstellungsbeschränkungen:Die gewählte Stapelreihenfolge sollte die Möglichkeiten und Einschränkungen des PCB-Herstellungsprozesses berücksichtigen, wie z. B. Materialverfügbarkeit, Anzahl der Schichten, Bohrseitenverhältnis,und Ausrichtungsgenauigkeit.

d) Kostenoptimierung:Die Auswahl der Materialien, die Anzahl der Schichten und die Komplexität des Aufbaus sollten im Einklang mit dem Projektbudget stehen und gleichzeitig die erforderliche Leistung und Zuverlässigkeit gewährleisten.

1.3 Gängige Arten von Stapelsequenzen für 16-lagige Leiterplatten: Es gibt mehrere gängige Stapelsequenzen für 16-lagige Leiterplatten

PCB, je nach gewünschter Leistung und Anforderungen. Einige häufige Beispiele sind:

a) Symmetrische Stapelfolge:Bei dieser Sequenz werden Signalschichten symmetrisch zwischen Strom- und Erdungsschichten platziert, um eine gute Signalintegrität, minimales Übersprechen und eine ausgewogene Wärmeableitung zu erreichen.

b) Sequentielle Stapelreihenfolge:In dieser Reihenfolge liegen die Signalschichten der Reihe nach zwischen den Leistungs- und Erdungsschichten. Es bietet eine bessere Kontrolle über die Schichtanordnung und ist vorteilhaft für die Erfüllung spezifischer Anforderungen an die Signalintegrität.

c) Gemischte Stapelreihenfolge:Hierbei handelt es sich um eine Kombination aus symmetrischen und sequentiellen Stapelreihenfolgen. Es ermöglicht die individuelle Anpassung und Optimierung des Layups für bestimmte Teile der Platine.

d) Signalsensitive Stapelsequenz:Diese Sequenz platziert empfindliche Signalschichten näher an der Masseebene, um eine bessere Störfestigkeit und Isolierung zu erreichen.

2. Wichtige Überlegungen zur Auswahl der 16-Lagen-PCB-Stapelreihenfolge:

2.1 Überlegungen zur Signalintegrität und Leistungsintegrität:

Die Stapelreihenfolge hat einen erheblichen Einfluss auf die Signalintegrität und Leistungsintegrität der Platine. Die richtige Platzierung der Signal- und Strom-/Masseebenen ist entscheidend für die Minimierung des Risikos von Signalverzerrungen, Rauschen und elektromagnetischen Störungen. Zu den wichtigsten Überlegungen gehören:

a) Platzierung der Signalebene:Hochgeschwindigkeitssignalschichten sollten nahe an der Masseebene platziert werden, um einen Rückweg mit geringer Induktivität zu gewährleisten und die Rauschkopplung zu minimieren. Auch die Signalschichten sollten sorgfältig ausgelegt werden, um Signalversatz und Längenanpassung zu minimieren.

b) Verteilung der Leistungsebene:Die Stapelreihenfolge sollte eine angemessene Verteilung der Stromversorgungsebenen gewährleisten, um die Stromversorgungsintegrität zu unterstützen. Es sollten ausreichend Strom- und Erdungsebenen strategisch platziert werden, um Spannungsabfälle, Impedanzdiskontinuitäten und Rauschkopplung zu minimieren.

c) Entkopplungskondensatoren:Die richtige Platzierung der Entkopplungskondensatoren ist entscheidend, um eine angemessene Leistungsübertragung sicherzustellen und das Rauschen der Stromversorgung zu minimieren. Die Stapelreihenfolge sollte die Nähe und Nähe der Entkopplungskondensatoren zu den Leistungs- und Masseebenen gewährleisten.

2.2 Wärmemanagement und Wärmeableitung:

Ein effizientes Wärmemanagement ist entscheidend für die Gewährleistung der Zuverlässigkeit und Leistung von Leiterplatten. Bei der Stapelreihenfolge sollte die richtige Platzierung von Strom- und Masseebenen, thermischen Durchkontaktierungen und anderen Kühlmechanismen berücksichtigt werden. Wichtige Überlegungen sind:

a) Verteilung der Leistungsebene:Eine angemessene Verteilung der Strom- und Erdungsebenen im gesamten Stapel trägt dazu bei, die Wärme von empfindlichen Komponenten abzuleiten und sorgt für eine gleichmäßige Temperaturverteilung auf der gesamten Platine.

b) Thermische Vias:Die Stapelreihenfolge sollte eine effektive Platzierung der thermischen Durchkontaktierung ermöglichen, um die Wärmeableitung von der Innenschicht zur Außenschicht oder zum Kühlkörper zu erleichtern. Dadurch werden lokale Hotspots vermieden und eine effiziente Wärmeableitung gewährleistet.

c) Komponentenplatzierung:Bei der Stapelreihenfolge sollten die Anordnung und Nähe der Heizkomponenten berücksichtigt werden, um eine Überhitzung zu vermeiden. Auch die richtige Ausrichtung der Komponenten an Kühlmechanismen wie Kühlkörpern oder Lüftern sollte berücksichtigt werden.

2.3 Fertigungsbeschränkungen und Kostenoptimierung:

Bei der Stapelreihenfolge müssen Herstellungsbeschränkungen und Kostenoptimierung berücksichtigt werden, da diese eine wichtige Rolle für die Machbarkeit und Erschwinglichkeit der Platine spielen. Zu den Überlegungen gehören:

a) Materialverfügbarkeit:Die ausgewählte Stapelreihenfolge sollte mit der Verfügbarkeit der Materialien und ihrer Kompatibilität mit dem ausgewählten PCB-Herstellungsprozess übereinstimmen.

b) Anzahl der Schichten und Komplexität:Die Stapelreihenfolge sollte innerhalb der Einschränkungen des ausgewählten PCB-Herstellungsprozesses gestaltet werden und dabei Faktoren wie die Anzahl der Schichten, das Seitenverhältnis der Bohrer und die Ausrichtungsgenauigkeit berücksichtigen.

c) Kostenoptimierung:Die Stapelreihenfolge soll den Materialeinsatz optimieren und die Fertigungskomplexität reduzieren, ohne die erforderliche Leistung und Zuverlässigkeit zu beeinträchtigen. Ziel sollte es sein, die mit Materialverschwendung, Prozesskomplexität und Montage verbundenen Kosten zu minimieren.

2.4 Schichtausrichtung und Signalübersprechen:

Die Stapelsequenz sollte Probleme bei der Schichtausrichtung lösen und Signalübersprechen minimieren, das sich negativ auf die Signalintegrität auswirken kann. Wichtige Überlegungen sind:

a) Symmetrische Stapelung:Die symmetrische Stapelung der Signalschichten zwischen Leistungs- und Erdungsschichten trägt dazu bei, die Kopplung zu minimieren und Übersprechen zu reduzieren.

b) Differentialpaar-Routing:Die Stapelreihenfolge sollte eine ordnungsgemäße Ausrichtung der Signalschichten für eine effiziente Weiterleitung von Hochgeschwindigkeits-Differenzsignalen ermöglichen. Dies trägt dazu bei, die Signalintegrität aufrechtzuerhalten und Übersprechen zu minimieren.

c) Signaltrennung:Bei der Stapelreihenfolge sollte die Trennung empfindlicher analoger und digitaler Signale berücksichtigt werden, um Übersprechen und Interferenzen zu reduzieren.

2.5 Impedanzkontrolle und HF-/Mikrowellenintegration:

Bei HF-/Mikrowellenanwendungen ist die Stapelreihenfolge entscheidend, um eine ordnungsgemäße Impedanzkontrolle und -integration zu erreichen. Zu den wichtigsten Überlegungen gehören:

a) Kontrollierte Impedanz:Die Stapelreihenfolge sollte ein kontrolliertes Impedanzdesign unter Berücksichtigung von Faktoren wie Leiterbahnbreite, Dielektrikumsdicke und Schichtanordnung ermöglichen. Dies gewährleistet eine korrekte Signalausbreitung und Impedanzanpassung für HF-/Mikrowellensignale.

b) Platzierung der Signalschicht:HF-/Mikrowellensignale sollten strategisch nahe an der Außenschicht platziert werden, um Störungen durch andere Signale zu minimieren und eine bessere Signalausbreitung zu gewährleisten.

c) HF-Abschirmung:Die Stapelreihenfolge sollte die richtige Platzierung der Erdungs- und Abschirmungsschichten umfassen, um HF-/Mikrowellensignale zu isolieren und vor Störungen zu schützen.

3.Verbindungsmethoden zwischen den Schichten

3.1 Durchgangslöcher, Sacklöcher und vergrabene Löcher:

Vias werden häufig beim Design von Leiterplatten (PCB) als Mittel zur Verbindung verschiedener Schichten verwendet. Sie werden durch alle Schichten der Leiterplatte gebohrt und plattiert, um einen elektrischen Durchgang zu gewährleisten. Durchgangslöcher sorgen für eine starke elektrische Verbindung und sind relativ einfach herzustellen und zu reparieren. Sie erfordern jedoch größere Bohrergrößen, die wertvollen Platz auf der Leiterplatte beanspruchen und die Routing-Optionen einschränken.

Blind- und Buried-Vias sind alternative Zwischenschicht-Verbindungsmethoden, die Vorteile bei der Raumnutzung und Routing-Flexibilität bieten.

Blind Vias werden von der Leiterplattenoberfläche aus gebohrt und enden in den inneren Schichten, ohne durch alle Schichten zu verlaufen. Sie ermöglichen Verbindungen zwischen benachbarten Schichten, während tiefere Schichten unberührt bleiben. Dies ermöglicht eine effizientere Nutzung des Platinenplatzes und reduziert die Anzahl der Bohrlöcher. Buried Vias hingegen sind Löcher, die vollständig in den inneren Schichten der Leiterplatte eingeschlossen sind und sich nicht bis zu den äußeren Schichten erstrecken. Sie stellen Verbindungen zwischen inneren Schichten her, ohne die äußeren Schichten zu beeinträchtigen. Buried Vias haben im Vergleich zu Durchgangslöchern und Blind Vias größere platzsparende Vorteile, da sie keinen Platz in der Außenschicht beanspruchen.

Die Wahl der Durchgangslöcher, Blind Vias und Buried Vias hängt von den spezifischen Anforderungen des PCB-Designs ab. Durchgangslöcher werden typischerweise in einfacheren Designs oder dort verwendet, wo Robustheit und Reparierbarkeit im Vordergrund stehen. Bei Designs mit hoher Dichte, bei denen Platz ein entscheidender Faktor ist, wie etwa bei Handheld-Geräten, Smartphones und Laptops, werden blinde und vergrabene Durchkontaktierungen bevorzugt.

3.2 Mikroporen undHDI-Technologie:

Microvias sind Löcher mit kleinem Durchmesser (normalerweise weniger als 150 Mikrometer), die hochdichte Zwischenschichtverbindungen in Leiterplatten ermöglichen. Sie bieten erhebliche Vorteile in Bezug auf Miniaturisierung, Signalintegrität und Routing-Flexibilität.

Microvias können in zwei Typen unterteilt werden: Through-Hole-Microvias und Blind-Microvias. Microvias werden hergestellt, indem Löcher von der Oberseite der Leiterplatte gebohrt werden und sich durch alle Schichten erstrecken. Blinde Mikrovias erstrecken sich, wie der Name schon sagt, nur auf bestimmte innere Schichten und durchdringen nicht alle Schichten.

High-Density-Interconnect (HDI) ist eine Technologie, die Microvias und fortschrittliche Fertigungstechniken nutzt, um eine höhere Schaltkreisdichte und Leistung zu erreichen. Die HDI-Technologie ermöglicht die Platzierung kleinerer Komponenten und eine engere Verlegung, was zu kleineren Formfaktoren und höherer Signalintegrität führt. Die HDI-Technologie bietet gegenüber der herkömmlichen PCB-Technologie mehrere Vorteile im Hinblick auf Miniaturisierung, verbesserte Signalausbreitung, reduzierte Signalverzerrung und verbesserte Funktionalität. Es ermöglicht mehrschichtige Designs mit mehreren Mikrovias, wodurch die Verbindungslängen verkürzt und parasitäre Kapazitäten und Induktivitäten reduziert werden.

Die HDI-Technologie ermöglicht auch die Verwendung fortschrittlicher Materialien wie Hochfrequenzlaminate und dünne dielektrische Schichten, die für HF-/Mikrowellenanwendungen von entscheidender Bedeutung sind. Es bietet eine bessere Impedanzkontrolle, reduziert Signalverluste und sorgt für eine zuverlässige Hochgeschwindigkeitssignalübertragung.

3.3 Zwischenschichtverbindungsmaterialien und -prozesse:

Die Auswahl der Zwischenschichtverbindungsmaterialien und -techniken ist entscheidend für die Gewährleistung einer guten elektrischen Leistung, mechanischen Zuverlässigkeit und Herstellbarkeit von Leiterplatten. Einige häufig verwendete Zwischenschichtverbindungsmaterialien und -techniken sind:

a) Kupfer:Kupfer wird aufgrund seiner hervorragenden Leitfähigkeit und Lötbarkeit häufig in leitenden Schichten und Durchkontaktierungen von Leiterplatten verwendet. Normalerweise wird es auf das Loch aufplattiert, um eine zuverlässige elektrische Verbindung zu gewährleisten.

b) Löten:Löttechniken wie Wellenlöten oder Reflow-Löten werden häufig verwendet, um elektrische Verbindungen zwischen Durchgangslöchern auf Leiterplatten und anderen Bauteilen herzustellen. Tragen Sie Lötpaste auf die Durchkontaktierung auf und wenden Sie Hitze an, um das Lot zu schmelzen und eine zuverlässige Verbindung herzustellen.

c) Galvanisieren:Galvanische Techniken wie stromlose Verkupferung oder elektrolytisches Kupfer werden zur Beschichtung von Durchkontaktierungen eingesetzt, um die Leitfähigkeit zu verbessern und gute elektrische Verbindungen sicherzustellen.

d) Verklebung:Durch Verbindungstechniken wie Kleben oder Thermokompressionsbonden werden Schichtstrukturen miteinander verbunden und zuverlässige Verbindungen hergestellt.

e) Dielektrisches Material:Die Wahl des dielektrischen Materials für den Leiterplattenaufbau ist für Zwischenschichtverbindungen von entscheidender Bedeutung. Hochfrequenzlaminate wie FR-4- oder Rogers-Laminate werden häufig verwendet, um eine gute Signalintegrität sicherzustellen und Signalverluste zu minimieren.

3.4 Querschnittsgestaltung und Bedeutung:

Das Querschnittsdesign des PCB-Aufbaus bestimmt die elektrischen und mechanischen Eigenschaften der Verbindungen zwischen den Schichten. Zu den wichtigsten Überlegungen zur Querschnittsgestaltung gehören:

a) Schichtanordnung:Die Anordnung der Signal-, Leistungs- und Masseebenen innerhalb eines PCB-Aufbaus beeinflusst die Signalintegrität, die Leistungsintegrität und elektromagnetische Störungen (EMI). Die richtige Platzierung und Ausrichtung der Signalschichten mit den Strom- und Masseebenen trägt dazu bei, die Rauschkopplung zu minimieren und Rückwege mit geringer Induktivität sicherzustellen.

b) Impedanzkontrolle:Beim Querschnittsdesign sollten kontrollierte Impedanzanforderungen berücksichtigt werden, insbesondere für Hochgeschwindigkeits-Digital- oder HF-/Mikrowellensignale. Dies erfordert die geeignete Auswahl dielektrischer Materialien und Dicken, um die gewünschte charakteristische Impedanz zu erreichen.

c) Wärmemanagement:Bei der Querschnittsgestaltung sollten eine effektive Wärmeableitung und ein Wärmemanagement berücksichtigt werden. Die richtige Platzierung von Strom- und Masseebenen, thermischen Durchkontaktierungen und Komponenten mit Kühlmechanismen (z. B. Kühlkörper) trägt dazu bei, Wärme abzuleiten und optimale Betriebstemperaturen aufrechtzuerhalten.

d) Mechanische Zuverlässigkeit:Bei der Abschnittskonstruktion sollte die mechanische Zuverlässigkeit berücksichtigt werden, insbesondere bei Anwendungen, die thermischen Wechseln oder mechanischer Belastung ausgesetzt sein können. Die richtige Auswahl von Materialien, Verbindungstechniken und Aufbaukonfiguration trägt dazu bei, die strukturelle Integrität und Haltbarkeit der Leiterplatte sicherzustellen.

4. Designrichtlinien für 16-Lagen-PCB

4.1 Schichtzuordnung und -verteilung:

Beim Entwurf einer 16-Lagen-Leiterplatte ist es wichtig, die Lagen sorgfältig zuzuordnen und zu verteilen, um Leistung und Signalintegrität zu optimieren. Hier sind einige Richtlinien für die Stufenzuteilung

und Vertrieb:

Bestimmen Sie die Anzahl der erforderlichen Signalschichten:

Berücksichtigen Sie die Komplexität des Schaltungsdesigns und die Anzahl der Signale, die weitergeleitet werden müssen. Weisen Sie genügend Signalebenen zu, um alle erforderlichen Signale unterzubringen. Sorgen Sie für ausreichend Routing-Platz und vermeiden Sie zu vielStau. Boden- und Energieebenen zuweisen:

Weisen Sie den Erdungs- und Stromversorgungsebenen mindestens zwei innere Schichten zu. Eine Masseebene trägt dazu bei, eine stabile Referenz für Signale bereitzustellen und elektromagnetische Störungen (EMI) zu minimieren. Die Stromversorgungsebene stellt ein Stromverteilungsnetzwerk mit niedriger Impedanz bereit, das zur Minimierung von Spannungsabfällen beiträgt.

Separate empfindliche Signalschichten:

Abhängig von der Anwendung kann es erforderlich sein, empfindliche oder Hochgeschwindigkeitssignalschichten von verrauschten oder Hochleistungsschichten zu trennen, um Interferenzen und Übersprechen zu verhindern. Dies kann durch die Platzierung spezieller Erdungs- oder Stromversorgungsebenen dazwischen oder durch die Verwendung von Isolationsschichten erreicht werden.

Signalschichten gleichmäßig verteilen:

Verteilen Sie die Signalschichten gleichmäßig über den gesamten Platinenstapel, um die Kopplung zwischen benachbarten Signalen zu minimieren und die Signalintegrität aufrechtzuerhalten. Vermeiden Sie es, Signalschichten nebeneinander im selben Stapelbereich zu platzieren, um Übersprechen zwischen den Schichten zu minimieren.

Betrachten Sie Hochfrequenzsignale:

Wenn Ihr Design Hochfrequenzsignale enthält, sollten Sie erwägen, die Hochfrequenzsignalschichten näher an den äußeren Schichten zu platzieren, um Übertragungsleitungseffekte zu minimieren und Ausbreitungsverzögerungen zu reduzieren.

4.2 Routing und Signalrouting:

Routing und Signalverfolgungsdesign sind entscheidend, um die ordnungsgemäße Signalintegrität sicherzustellen und Störungen zu minimieren. Hier einige Richtlinien für Layout und Signalführung auf 16-Lagen-Leiterplatten:

Verwenden Sie breitere Leiterbahnen für Hochstromsignale:

Verwenden Sie für Signale, die hohen Strom führen, wie z. B. Strom- und Erdungsanschlüsse, breitere Leiterbahnen, um Widerstand und Spannungsabfall zu minimieren.

Passende Impedanz für Hochgeschwindigkeitssignale:

Stellen Sie bei Hochgeschwindigkeitssignalen sicher, dass die Leiterbahnimpedanz mit der charakteristischen Impedanz der Übertragungsleitung übereinstimmt, um Reflexionen und Signaldämpfung zu verhindern. Verwenden Sie kontrollierte Impedanzdesigntechniken und korrekte Berechnungen der Leiterbahnbreite.

Minimieren Sie Leiterbahnlängen und Kreuzungspunkte:

Halten Sie die Leiterbahnlängen so kurz wie möglich und reduzieren Sie die Anzahl der Kreuzungspunkte, um parasitäre Kapazitäten, Induktivitäten und Interferenzen zu reduzieren. Optimieren Sie die Platzierung der Komponenten und verwenden Sie spezielle Routing-Ebenen, um lange, komplexe Leiterbahnen zu vermeiden.

Separate High-Speed- und Low-Speed-Signale:

Trennen Sie Hochgeschwindigkeits- und Niedriggeschwindigkeitssignale, um die Auswirkungen von Rauschen auf Hochgeschwindigkeitssignale zu minimieren. Platzieren Sie Hochgeschwindigkeitssignale auf dedizierten Signalebenen und halten Sie sie von leistungsstarken oder verrauschten Komponenten fern.

Verwenden Sie Differenzpaare für Hochgeschwindigkeitssignale:

Um Rauschen zu minimieren und die Signalintegrität für Hochgeschwindigkeits-Differenzsignale aufrechtzuerhalten, verwenden Sie Routing-Techniken für Differenzpaare. Halten Sie die Impedanz und Länge der Differenzialpaare aufeinander abgestimmt, um Signalversatz und Übersprechen zu verhindern.

4.3 Verteilung der Erdschicht und der Leistungsschicht:

Die richtige Verteilung der Erdungs- und Stromversorgungsebenen ist entscheidend für die Erzielung einer guten Stromversorgungsintegrität und die Reduzierung elektromagnetischer Störungen. Hier sind einige Richtlinien für die Zuweisung von Masse- und Stromversorgungsebenen auf 16-Lagen-Leiterplatten:

Weisen Sie dedizierte Boden- und Antriebsflugzeuge zu:

Weisen Sie mindestens zwei innere Schichten für dedizierte Erdungs- und Stromversorgungsebenen zu. Dies trägt dazu bei, Erdschleifen zu minimieren, EMI zu reduzieren und einen Rückweg mit niedriger Impedanz für Hochfrequenzsignale bereitzustellen.

Separate digitale und analoge Masseebenen:

Wenn das Design über digitale und analoge Abschnitte verfügt, wird empfohlen, für jeden Abschnitt separate Masseebenen zu verwenden. Dies trägt dazu bei, die Rauschkopplung zwischen den digitalen und analogen Abschnitten zu minimieren und die Signalintegrität zu verbessern.

Platzieren Sie Erdungs- und Stromversorgungsebenen in der Nähe von Signalebenen:

Platzieren Sie Erdungs- und Stromversorgungsebenen in der Nähe der von ihnen gespeisten Signalebenen, um die Schleifenfläche zu minimieren und die Rauschaufnahme zu reduzieren.

Verwenden Sie mehrere Vias für Powerplanes:

Verwenden Sie mehrere Durchkontaktierungen, um die Leistungsebenen zu verbinden, um die Leistung gleichmäßig zu verteilen und die Impedanz der Leistungsebenen zu reduzieren. Dadurch werden Versorgungsspannungsabfälle minimiert und die Stromversorgungsintegrität verbessert.

Enge Hälse in Motorflugzeugen vermeiden:

Vermeiden Sie schmale Hälse in Leistungsplatinen, da diese zu Stromstau führen und den Widerstand erhöhen können, was zu Spannungsabfällen und Ineffizienzen der Leistungsplatine führt. Nutzen Sie starke Verbindungen zwischen verschiedenen Power-Plane-Bereichen.

4.4 Platzierung des Wärmeleitpads und der Durchkontaktierung:

Die richtige Platzierung von Wärmeleitpads und Durchkontaktierungen ist entscheidend, um die Wärme effektiv abzuleiten und eine Überhitzung der Komponenten zu verhindern. Hier sind einige Richtlinien für die Platzierung von Wärmeleitpads und Durchkontaktierungen auf 16-lagigen Leiterplatten:

Wärmeleitpad unter wärmeerzeugende Bauteile legen:

Identifizieren Sie die wärmeerzeugende Komponente (z. B. einen Leistungsverstärker oder einen Hochleistungs-IC) und platzieren Sie das Wärmeleitpad direkt darunter. Diese Wärmeleitpads bieten einen direkten Wärmepfad zur Wärmeübertragung auf die innere Wärmeschicht.

Verwenden Sie mehrere thermische Durchkontaktierungen zur Wärmeableitung:

Verwenden Sie mehrere thermische Durchkontaktierungen, um die Wärmeschicht und die Außenschicht zu verbinden und so eine effiziente Wärmeableitung zu gewährleisten. Diese Durchkontaktierungen können in einem versetzten Muster um das Wärmeleitpad herum platziert werden, um eine gleichmäßige Wärmeverteilung zu erreichen.

Berücksichtigen Sie die thermische Impedanz und den Schichtaufbau:

Berücksichtigen Sie beim Entwerfen von thermischen Durchkontaktierungen die thermische Impedanz des Platinenmaterials und des Lagenaufbaus. Optimieren Sie Durchkontaktierungsgröße und -abstand, um den Wärmewiderstand zu minimieren und die Wärmeableitung zu maximieren.

4.5 Komponentenplatzierung und Signalintegrität:

Die richtige Platzierung der Komponenten ist entscheidend für die Aufrechterhaltung der Signalintegrität und die Minimierung von Störungen. Hier sind einige Richtlinien für die Platzierung von Komponenten auf einer 16-Lagen-Leiterplatte:

Gruppenbezogene Komponenten:

Gruppieren Sie verwandte Komponenten, die Teil desselben Subsystems sind oder starke elektrische Wechselwirkungen aufweisen. Dies reduziert die Leiterbahnlänge und minimiert die Signaldämpfung.

Halten Sie Hochgeschwindigkeitskomponenten in der Nähe:

Platzieren Sie Hochgeschwindigkeitskomponenten wie Hochfrequenzoszillatoren oder Mikrocontroller nahe beieinander, um die Leiterbahnlängen zu minimieren und eine ordnungsgemäße Signalintegrität sicherzustellen.

Minimieren Sie die Spurlänge kritischer Signale:

Minimieren Sie die Leiterbahnlänge kritischer Signale, um Ausbreitungsverzögerung und Signaldämpfung zu reduzieren. Platzieren Sie diese Komponenten so nah wie möglich.

Empfindliche Komponenten trennen:

Trennen Sie rauschempfindliche Komponenten, wie z. B. analoge Komponenten oder Low-Level-Sensoren, von leistungsstarken oder verrauschten Komponenten, um Interferenzen zu minimieren und die Signalintegrität aufrechtzuerhalten.

Erwägen Sie Entkopplungskondensatoren:

Platzieren Sie Entkopplungskondensatoren so nah wie möglich an den Stromanschlüssen jeder Komponente, um sauberen Strom zu liefern und Spannungsschwankungen zu minimieren. Diese Kondensatoren helfen, die Stromversorgung zu stabilisieren und die Rauschkopplung zu reduzieren.

5. Simulations- und Analysetools für Stack-Up-Design

5.1 3D-Modellierungs- und Simulationssoftware:

3D-Modellierungs- und Simulationssoftware ist ein wichtiges Werkzeug für das Stackup-Design, da sie es Designern ermöglicht, virtuelle Darstellungen von PCB-Stackups zu erstellen. Die Software kann Schichten, Komponenten und deren physikalische Wechselwirkungen visualisieren. Durch die Simulation des Stapelaufbaus können Entwickler potenzielle Probleme wie Signalübersprechen, EMI und mechanische Einschränkungen identifizieren. Es hilft auch, die Anordnung der Komponenten zu überprüfen und das gesamte PCB-Design zu optimieren.

5.2 Tools zur Signalintegritätsanalyse:

Werkzeuge zur Analyse der Signalintegrität sind für die Analyse und Optimierung der elektrischen Leistung von Leiterplattenaufbauten von entscheidender Bedeutung. Diese Tools nutzen mathematische Algorithmen zur Simulation und Analyse des Signalverhaltens, einschließlich Impedanzkontrolle, Signalreflexionen und Rauschkopplung. Durch die Durchführung von Simulationen und Analysen können Designer potenzielle Probleme mit der Signalintegrität frühzeitig im Designprozess erkennen und notwendige Anpassungen vornehmen, um eine zuverlässige Signalübertragung sicherzustellen.

5.3 Werkzeuge zur thermischen Analyse:

Werkzeuge zur thermischen Analyse spielen eine wichtige Rolle beim Stackup-Design, indem sie das Wärmemanagement von Leiterplatten analysieren und optimieren. Diese Werkzeuge simulieren die Wärmeableitung und Temperaturverteilung innerhalb jeder Schicht des Stapels. Durch die genaue Modellierung der Verlustleistung und der Wärmeübertragungspfade können Designer Hotspots identifizieren, die Platzierung von Kupferschichten und thermischen Durchkontaktierungen optimieren und eine ordnungsgemäße Kühlung kritischer Komponenten sicherstellen.

5.4 Design für Herstellbarkeit:

Design für Herstellbarkeit ist ein wichtiger Aspekt des Stackup-Designs. Es stehen verschiedene Softwaretools zur Verfügung, die dazu beitragen können, dass der ausgewählte Stapel effizient hergestellt werden kann. Diese Tools liefern Feedback zur Machbarkeit des gewünschten Aufbaus unter Berücksichtigung von Faktoren wie Materialverfügbarkeit, Schichtdicke, Herstellungsprozess und Herstellungskosten. Sie helfen Designern dabei, fundierte Entscheidungen zur Optimierung der Stapelung zu treffen, um die Herstellung zu vereinfachen, das Risiko von Verzögerungen zu verringern und die Ausbeute zu steigern.

6.Schritt-für-Schritt-Designprozess für 16-Lagen-Leiterplatten

6.1 Erstbedarfserfassung:

Sammeln Sie in diesem Schritt alle notwendigen Anforderungen für das 16-Lagen-PCB-Design. Verstehen Sie die Funktionalität der Leiterplatte, die erforderliche elektrische Leistung, mechanische Einschränkungen und alle spezifischen Designrichtlinien oder -standards, die befolgt werden müssen.

6.2 Komponentenzuordnung und -anordnung:

Ordnen Sie Bauteile je nach Bedarf auf der Leiterplatte zu und legen Sie deren Anordnung fest. Berücksichtigen Sie Faktoren wie Signalintegrität, thermische Überlegungen und mechanische Einschränkungen. Gruppieren Sie Komponenten nach elektrischen Eigenschaften und platzieren Sie sie strategisch auf der Platine, um Störungen zu minimieren und den Signalfluss zu optimieren.

6.3 Stapelaufbau und Lagenverteilung:

Bestimmen Sie das Stapeldesign für die 16-Lagen-Leiterplatte. Berücksichtigen Sie bei der Auswahl des geeigneten Materials Faktoren wie Dielektrizitätskonstante, Wärmeleitfähigkeit und Kosten. Weisen Sie Signal-, Strom- und Masseebenen entsprechend den elektrischen Anforderungen zu. Platzieren Sie Erdungs- und Stromversorgungsebenen symmetrisch, um einen ausgeglichenen Stapel zu gewährleisten und die Signalintegrität zu verbessern.

6.4 Signalrouting und Routing-Optimierung:

In diesem Schritt werden Signalspuren zwischen Komponenten geleitet, um eine ordnungsgemäße Impedanzkontrolle und Signalintegrität sicherzustellen und Signalübersprechen zu minimieren. Optimieren Sie das Routing, um die Länge kritischer Signale zu minimieren, das Überqueren sensibler Leiterbahnen zu vermeiden und die Trennung zwischen Hochgeschwindigkeits- und Niedriggeschwindigkeitssignalen aufrechtzuerhalten. Verwenden Sie bei Bedarf Differenzialpaare und Routingtechniken mit kontrollierter Impedanz.

6.5 Interlayer-Verbindungen und Via-Platzierung:

Planen Sie die Platzierung der Verbindungsdurchkontakte zwischen den Schichten. Bestimmen Sie anhand von Schichtübergängen und Komponentenverbindungen den geeigneten Durchgangstyp, z. B. Durchgangsloch oder Sackloch. Optimieren Sie das Via-Layout, um Signalreflexionen und Impedanzdiskontinuitäten zu minimieren und eine gleichmäßige Verteilung auf der Leiterplatte aufrechtzuerhalten.

6.6 Endgültige Designüberprüfung und Simulation:

Vor der Fertigung werden abschließende Designüberprüfungen und Simulationen durchgeführt. Verwenden Sie Simulationstools, um PCB-Designs auf Signalintegrität, Leistungsintegrität, thermisches Verhalten und Herstellbarkeit zu analysieren. Überprüfen Sie das Design anhand der ursprünglichen Anforderungen und nehmen Sie die erforderlichen Anpassungen vor, um die Leistung zu optimieren und die Herstellbarkeit sicherzustellen.

Arbeiten Sie während des gesamten Designprozesses mit anderen Stakeholdern wie Elektroingenieuren, Maschinenbauingenieuren und Fertigungsteams zusammen und kommunizieren Sie mit ihnen, um sicherzustellen, dass alle Anforderungen erfüllt und potenzielle Probleme gelöst werden. Überprüfen und iterieren Sie Entwürfe regelmäßig, um Feedback und Verbesserungen einzubeziehen.

7. Best Practices und Fallstudien der Branche

7.1 Erfolgreiche Fälle von 16-Lagen-PCB-Design:

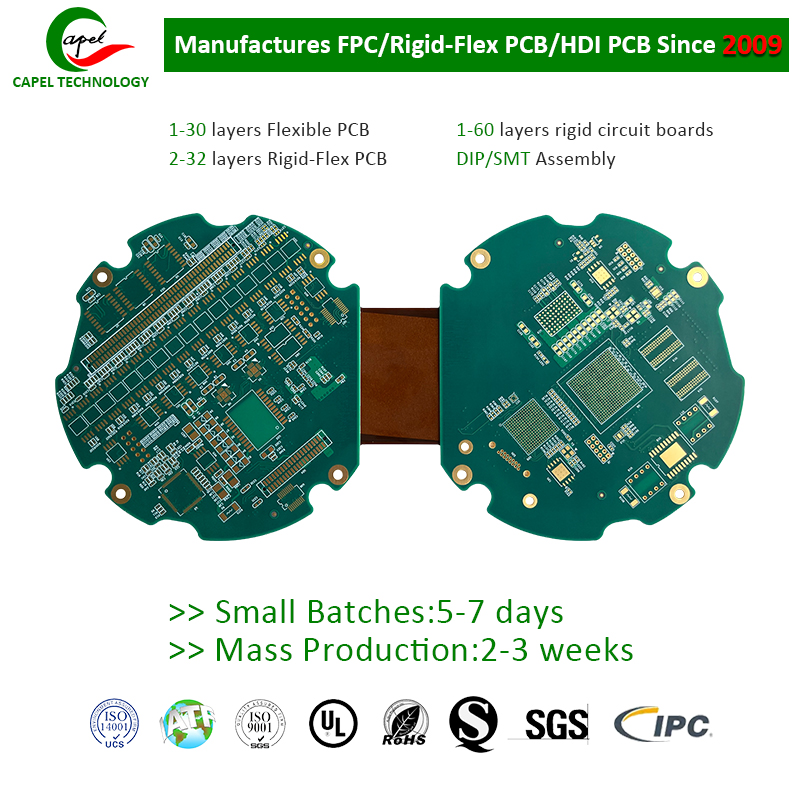

Fallstudie 1:Shenzhen Capel Technology Co., Ltd. hat erfolgreich eine 16-lagige Leiterplatte für Hochgeschwindigkeitsnetzwerkgeräte entwickelt. Durch sorgfältige Berücksichtigung der Signalintegrität und Stromverteilung erzielen sie eine überragende Leistung und minimieren elektromagnetische Störungen. Der Schlüssel zu ihrem Erfolg ist ein vollständig optimiertes Stapeldesign mit kontrollierter Impedanz-Routing-Technologie.

Fallstudie 2:Shenzhen Capel Technology Co., Ltd. hat eine 16-lagige Leiterplatte für ein komplexes medizinisches Gerät entwickelt. Durch die Verwendung einer Kombination aus oberflächenmontierten und durchsteckbaren Komponenten erreichten sie ein kompaktes und dennoch leistungsstarkes Design. Sorgfältige Komponentenplatzierung und effizientes Routing sorgen für hervorragende Signalintegrität und Zuverlässigkeit.

7.2 Aus Fehlern lernen und Fallstricke vermeiden:

Fallstudie 1:Einige Leiterplattenhersteller stießen beim 16-lagigen Leiterplattendesign von Kommunikationsgeräten auf Probleme mit der Signalintegrität. Die Gründe für das Scheitern waren unzureichende Berücksichtigung der Impedanzkontrolle und das Fehlen einer ordnungsgemäßen Masseebenenverteilung. Die daraus gewonnene Lektion besteht darin, die Anforderungen an die Signalintegrität sorgfältig zu analysieren und strenge Designrichtlinien für die Impedanzkontrolle durchzusetzen.

Fallstudie 2:Aufgrund der Komplexität des Designs standen einige Leiterplattenhersteller bei der Herstellung ihrer 16-lagigen Leiterplatte vor Herausforderungen. Der übermäßige Einsatz von Blind Vias und dicht gepackten Komponenten führt zu Herstellungs- und Montageschwierigkeiten. Die daraus gewonnene Lektion besteht darin, angesichts der Fähigkeiten des ausgewählten Leiterplattenherstellers ein Gleichgewicht zwischen Designkomplexität und Herstellbarkeit zu finden.

Um Fallstricke und Fallstricke beim 16-Lagen-PCB-Design zu vermeiden, ist es entscheidend:

a. Die Anforderungen und Einschränkungen des Entwurfs genau verstehen.

b.Gestapelte Konfigurationen, die die Signalintegrität und Stromverteilung optimieren. c. Komponenten sorgfältig verteilen und anordnen, um die Leistung zu optimieren und die Herstellung zu vereinfachen.

d.Stellen Sie geeignete Routing-Techniken sicher, z. B. die Kontrolle der Impedanz und die Vermeidung der übermäßigen Verwendung von Blind Vias.

e. Arbeiten Sie effektiv mit allen am Designprozess beteiligten Beteiligten zusammen, einschließlich Elektro- und Maschinenbauingenieuren sowie Fertigungsteams.

f. Führen Sie eine umfassende Designüberprüfung und Simulation durch, um potenzielle Probleme vor der Herstellung zu identifizieren und zu beheben.

Zeitpunkt der Veröffentlichung: 26.09.2023

Zurück